# **Chapter 20**

# Vacuum Tubes - The First Active Devices

*Active* devices refer to those things that can electronically *control* electron flow. The first active devices were vacuum tubes, followed by the *transistor junction*. This chapter begins the fist active devices and their development into increasingly more complex device that made all electronics possible.

# In the Beginning: the Fleming Valve

The first such devices were *diodes* (of a sort), double-electrode structures that would allow electron flow to go only one way from a heated filament to a *plate*. Although technically they were half-wave *rectifiers*, they worked slightly better than a variety of diode-like devices loosely based on semiconducting junctions as *detectors* of broadband damped-wave on-off-keyed radio signals.<sup>1</sup>. A *new* device back around the year 1900 was the *galena crystal*, a rather crude point-contact solid-state diode.<sup>2</sup>

English academician John Ambrose Fleming experimentally developed the first vacuum tube diode about 1888 while investigating the *Edison Effect* mentioned in 1883 literature. The first *Fleming valve* has been described as an Edison incandescent lamp with a metal cylinder around it. The glowing filament acted to emit electrons, some of which would go to the cylinder, later called a *plate*. Electrons would be repulsed by the high temperature of the filament so electron flow would always be from filament to plate. The English used *valve* as a descriptor for this new device since it was, in effect, a one-way *valve* for electrons. Americans adopted the name *tube* probably because the first valves formed in the USA were made from glass tubing.

The key to *valve* or *tube* operation was the *vacuum* inside it. Electrons would literally move around in a vacuum whereas they would be physically inhibited by another substance such as air. The *Fleming Valve* was tried out in early Marconi receivers and it worked better than the other strange devices used before that. While this Fleming Valve worked better, the 'radio receivers' of early days were little more than *tuned half-wave rectifiers*. That would change about 1906 when Lee De Forest began some experiments of his own.

<sup>&</sup>lt;sup>1</sup> A variety of such semiconducting junctions existed before 1900, nearly all of them quite inefficient but better than nothing at all. There was no theory to back up their applications and all inventions in radio of those early days was empirical.

<sup>&</sup>lt;sup>2</sup> That gave birth to numerous new names and catch-phrases, such as *cats whisker*, a holder for a needle that was manually positioned on an exposed surface of the crystal held in a molded lead base. Once that location was found, the user was said to have found the *sweet spot*. Crude receivers were, and still are, called *Crystal Sets*.

# The First True Active Device

De Forest introduced a third electrode in the space between filament and plate, a literal wire *grid*. When this *grid* was at a potential (or voltage) more negative than the filament, few electrons would flow into it. If the relative grid voltage was less negative, more electrons would flow from the filament *cathode* through the grid to the plate or *anode*. Voltage on the grid (relative to the filament) *could control the electron flow from filament to plate*. Not only that, the grid, the third electrode, would draw very little electron current when negatively biased. It was an ideal amplifier!

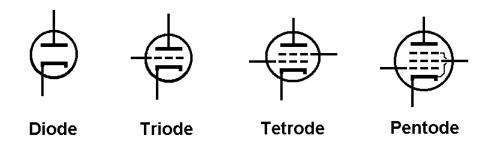

Lee De Forest called his new invention an *audion*, supposedly a contraction of two other words, in his January 1906 patent. In a later improvement patent application, De Forest called it a *De Forest Triode*, possibly to get away from the early name pertaining to audio frequencies. This was a forerunner to more tube descriptions having multiple grids: Tetrode with two grids, Pentode with three grids, even Pentagrid having five grids.<sup>3</sup>

In all circuits that followed, vacuum tube plates would always be connected to a *positive* supply voltage relative to the filament.<sup>4</sup> In very old radio receivers powered by batteries, the filaments were lit by an A battery of low voltage, a B battery for high voltage plate supply, and, perhaps, a C battery for low current demand biasing. Since the plate supply is always positive, the high voltage battery was colloquially called B+, spoken as B-Plus, in common use in electronics labs as late as the 1980s.

# Application

The first application of this new triode to radio was probably as an audio amplifier, to increase the audio out of those tuned half-wave rectifier circuits called receivers. Audio frequencies were comfortable experimental areas. One of the first things noted was that all vacuum tube circuits *invert* their amplified voltages. Applications as RF amplifiers were few and far between at the beginning. Everyone had to know more about basic components, resonance, impedance, and so forth and there wasn't a lot of *term standardization* in the first quarter of the 1900s. De Forest thought that the principles of his new audion or triode were due to trace gasses in his vacuum. Another inventor, Irving Langmuir, would correctly say that the vacuum itself was responsible.

The first RF circuit applications took advantage of the high impedance of negatively-biased grids. Those grids drew so little power that they appeared as *high impedance loads* to any source. This was good for tuned-RF circuits since a high-impedance load did not degrade the Q of a tuned circuit.

An early experimenter, Edwin Howard Armstrong, would begin his revolutionary inventions with the *regenerative detector* that replaced the old crystal set receivers. Armstrong used *positive feedback* to increase the sensitivity of his detector at least a hundred times more than was possible with the half-wave rectifier detector of beginning radio days. Armstrong's detector was essentially unstable, best sensitivity a bit short of being an actual oscillator. So close to being oscillatory that

<sup>&</sup>lt;sup>3</sup> Tetrodes and Pentodes count the filament and plate in number of electrodes. By the time of the Pentagrid, the name assigners probably ran out of descriptive names.

<sup>&</sup>lt;sup>4</sup> Using transistor terms, vacuum tubes always worked similar to NPN transistors.

a feedback or *regeneration* control was necessary for the user to adjust. Despite its so-called shortcomings, it was a remarkable improvement in sensitivity and literally opened the world of radio to more distant communication ranges. The telephone infrastructure was also experimenting, but with *negative feedback* to both stabilize amplification and remove much non-linear distortion.

# Overview

# **Standardizing How Vacuum Tubes Work**

In the approximate two decades after 1906, thinking people started to change some of the names and terminology as well as improving the technology of making them. That was due to academicians and manufacturers. Academicians wanted *analytical models* so they could design circuits mathematically. Manufacturers wanted better performance or, of more importance, *repeatability in specifications* of what they manufactured. To suit the latter, the filament was encased in a coated sleeve with the coating able to coax more electrons being emitted. That was called the *cathode* and the filament of this *indirectly-heated cathode* tube type was called a *heater*. The plate was interchangeably called *anode* or just *plate*. Grids were called just that but, beyond the first or *control grid*, they had prefixes such as *screen grid* for the second one, *suppressor grid* for the third one. The first Fleming Valve fell into the *directly-heated cathode* category. That directly-heated tube variety would remain with the low-temperature, low-voltage filaments of so-called *battery tubes* used in portable radios until up into the 1960s.

Figure 20-1 Four principal types of vacuum tubes in standardized symbolic form for indirectly-heated cathode types. Electron flow is from cathode (at bottom) to plate (at top) with *grids* between the two on Triode through Pentode. The *control grid* is physically closest to cathode, has greatest influence in cathode-to-plate current control.

To set up analytical models, three new terms were devised called *dynamic characteristics*. These could be used by circuit designers to approximate actual operation with tubes and hardware.

**Transconductance**, abbreviated **gm**, is the small-scale change in plate current due to a small-scale change in grid voltage. The term **small-scale** is just that, a tiny change in one electrode induced to effect a tiny change in another electrode's characteristics. *Transconductance* and the plate output loading can be the determinator of tube stage voltage gain in analytical models.

*Plate Resistance*, abbreviated  $r_{p}$ , is the small-scale change in plate voltage divided by the

small-scale change in plate current, and expressed in terms of Ohms. In analytical models of linear amplifier models, plate resistance appears as the equivalent of a high-value resistor in parallel with the plate load impedance. Most modern pentodes will have plate resistance values of 200 KOhms or larger.

Amplification Factor, abbreviated  $\mu$ , is the small-scale change in plate voltage from a smallscale change in grid voltage, all other electrodes and currents being kept constant. Note: The term *small-scale* is just that, peak-to-peak values something between very small to right down to noise level, values depending on the measurement AC voltmeters and AC ammeters. Dynamic characteristics are measured at AC, *plate tube curves* seen on many tube datasheets, done at DC.

Vacuum tube plate characteristics at DC are somewhat non-linear. Some tubes are deliberately designed to have non-linear *transconductance* for the purpose of controlling stage gain by means of negative DC bias on the grid. In using *small-scale dynamic characteristics*, it is possible to closely approximate actual hardware performance with different DC bias conditions.

# **Directly-Heated Cathodes versus Indirectly-Heated Cathodes**

The first triodes were directly-heated. That is, their heater-filament was the cathode. Not too long after that, filaments became indirectly-heated by having a tubular sleeve over the heater-filament, the sleeve being the cathode itself. In addition, both types of heater-filaments were coated with a material to yield greater electron flow from these cathodes.

By separating the heater-filament from the cathode sleeve, the indirectly-heated heater-filament became the tube of choice for ready-made circuitry. The heater could be isolated from the cathode in the circuit and this prompted new tubes with the same characteristics as the old ones but with different filament voltages. The *All-American Five* transformerless table-top broadcast receiver was born, all filaments taking the same current of 150 mA and all in series (with a pilot lamp) so that their filament voltages added up to about 129 VAC RMS. Plate and screen high voltage was supplied by a half-wave rectifier directly from the AC line voltage.<sup>5</sup>

With the indirectly-heated cathode there was the advantage of keeping the filament supply away from the vacuum tube itself. If nothing else, the filaments could be capacitively bypassed to ground to remove them from the circuits. In general, the indirectly-heated cathodes resulted in slightly more uniform characteristics.

Directly-heated filament tubes remained for the dry-cell-powered battery receivers and other instruments using a B+ of at least 67 VDC (usually 90 VDC) but with filaments of only 1.5 VDC. With directly-heated cathodes the designers had to contend with characteristics that were modified for biasing by the 1.5 VDC gradient along each cathode surface. Those gradients did not exist in indirectly-heated cathodes. Fortunately, this was a minor problem and could be overcome in most cases.

<sup>&</sup>lt;sup>5</sup> The usual octal-based tube line-up was a 12SA7 pentagrid as both LO and mixer, a 12SK7 as an IF amplifier, and (usually) a 12.6 VAC filament dual-diode triode as detector, AGC rectifier, and audio voltage amplifier plus a 50 VAC filament audio speaker driver and a 35 VAC filament half-wave rectifier. For 7-pin miniature glass envelopes, the 12BE6, 12BA6, 12AT6, 50B5, and 35Z5 were circuit-complimentary for the same functions. Literally millions of these transformerless AM broadcast receivers were made starting just before WWII and continuing on for two decades after WWII was over. There was very little change between models insofar as the point-to-point wiring was concerned..

# **General Operation for Biasing**

The general naming of USA-designed tube types comes from the total number of electrodes of a tube. The *control grid* (or just plain *grid*) has the most pronounced control over cathode-plate current. In the Pentode, the last grid, called the *suppressor grid*, is usually connected internally to the cathode although a few types have the suppressor brought out as a separate pin.<sup>6</sup> The second grid of Tetrodes and Pentodes is called the *screen grid* (or just *screen*) and has an effect on the cathode-plate current but generally kept at a specific DC supply voltage as indicated in vacuum tube data sheets. In most Pentodes, the third grid is called the *suppressor* and is generally there to reduce the effect of secondary emission of electrons striking the plate and bouncing off. Most suppressor grids are connected internally to the cathode.

Most Diodes in-use are *dual-plate, directly-heated-cathode types* (example a type 5Y3) for full-wave DC power rectification from a center-tapped power supply transformer secondary. Old FM receiver demodulators are generally dual-diodes (such as the 6AL5 or 6H6) having isolated diodes but with common filament-heaters.

# Self-Bias Through a Single Resistor

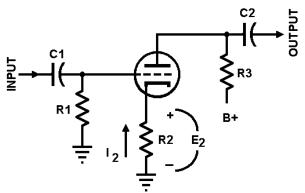

Figure 20-2 is the general form of self-bias of a single triode voltage amplifier running with low signal input and output RMS voltages. The cathode-plate current passes through R2 and creates a voltage drop (E2). That voltage drop is the bias of control grid to cathode..

The grid input is normally sitting at common potential or zero Volts via R1. As far as the triode is concerned, E2 provides a slight *negative* potential to the grid on a relative basis. Note the electron current flow direction represented by I2; *relative* to the cathode, the grid has a slight negative voltage.

Figure 20-2 A triode connected for selfbias via voltage drop across R2

Series resistor R2 may or may not be bypassed by a capacitor to ground. That is dependent on the circuit design. That capacitor must have a value such that its reactive impedance is low at the lowest signal voltage frequency in order to bypass R2. If R2 is not bypassed, then it becomes a signal amplification *loss*. That loss can be taken as an improvement on reducing distortion from the unbypassed cathode resistors. This is shown by:

<sup>&</sup>lt;sup>6</sup> The purpose of the suppressor grid was to reduce the *secondary emission of electrons* from the plate and this distorting the plate current characteristics. In certain tube types the suppressor grid has been used as an amplitude modulator for transmitters in older designs, mainly to reduce the number of tubes used. Cathode-to-plate current at higher voltages without a suppressor grid would tend to make the higher electron velocity cause a *bouncing off* of electrons called secondary emission.

$A_{V} = \frac{A}{(1 + b A)}$  where: (20-2) A = Voltage gain without feedback  $A_{V} = Voltage gain with feedback$  b = Percentage of feedback (can be = to b / R3) whereR3 equals the plate load.

For the difference between *feedback* and none at all, take the percent of the cathode series resistance divided by the total plate load in Ohms. If there is no cathode resistance, then the numerator becomes 1 and the  $A_v$  becomes the same as A. If there is a cathode resistance, then divide it by the total plate load resistance to obtain the value of b.

Assume a tube has an A of 100, total  $R_L$  of 10 KOhms and would have a cathode resistance of 220 Ohms. Value of b would be  $22 \times 10^{-3}$  and (b x A) would be 2.2. Total value of  $A_V$  would be 31.25 times voltage gain instead of the no-cathode-resistance case of 100 times.

Distortion reduction will work with any vacuum tube having a grid and with an unbypassed cathode resistor. It will not work with tube diodes since those have no grid to accept an input.<sup>7</sup> Actual distortion reduction *must be measured* since there are too many things to consider as to the cause of the bypassed self-bias resistor distortion.

#### **Voltage Gain Amount**

Voltage amplification with pentodes is quite easy. As a general rule, one can simply multiply the transconductance  $(g_M)$  by the load impedance. End result is the voltage gain for that stage. To be slightly more accurate, the load impedance would be in parallel with the plate resistance  $(r_P)$ .

Voltage Gain =

$$V_{OUT} / V_{IN}$$

= transconductance x ( $Z_{LOAD} || r_P$ ) (20-3)

If the load impedance (such as mid-band filter impedance) is known, then that simple formula is within  $\pm 5\%$  of the correct value.

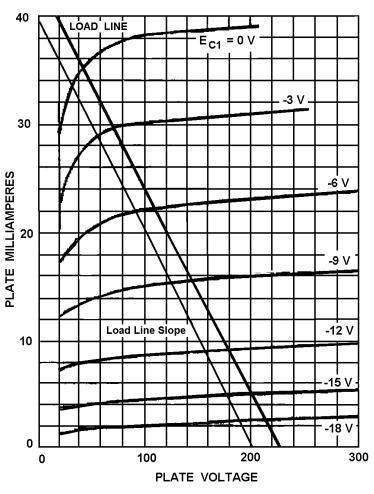

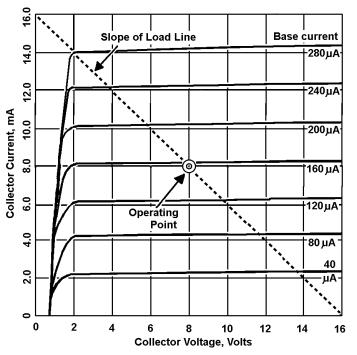

For triodes and some tetrodes this might be too coarse. In that case, a *load line* can be drawn on characteristic plate voltage and current curves (on datasheets) relative to the control grid bias voltage. See Figure 20-3 for the steps involved. It is quite simple. The *slope* of the straight load line begins at top left for zero plate voltage and ends at bottom right at maximum plate voltage but with zero plate current. Angle of the slope is equal to plate voltage divided by the load impedance to achieve the plate current with no voltage.

If the load impedance is 5000 Ohms, divide a convenient plate voltage (such as 200 VDC) by that to get 40 mA. See the dotted line in Figure 20-3 for that load line slope. Slide the load line

<sup>&</sup>lt;sup>7</sup> Some diode circuits have the *appearance* of something similar to unbypassed self-bias resistors but those are generally for another reason.

(without changing its slope) left or right until the load line intersects a desired control grid voltage (such as -9 VDC for a 6AK6 pentode). That intersection is the bias for the grid and all signal inputs vary away from that bias level.

To find the resulting  $V_{OUT}$  for a particular  $V_{IN}$ , use the load line intersection to see the  $V_{OUT}$  from the x-axis scale at the bottom. This was already done for the 6AK6 audio speaker driver in Chapter 63 (using a slightly different plate characteristic curve set) for a -9 VDC bias point.

At the intersection of the Load Line and plate current curves, the control-grid to cathode voltages are:

| E <sub>C1-CATHODE</sub> | Plate Voltage |  |  |

|-------------------------|---------------|--|--|

| 0 V                     | 40            |  |  |

| -3 V                    | 68            |  |  |

| -6 V                    | 104           |  |  |

| -9 V                    | 135           |  |  |

| -12 V                   | 170           |  |  |

| -15 V                   | 192           |  |  |

| -18 V                   | 205           |  |  |

|                         |               |  |  |

Figure 20-3 Load Line construction done for a 6AK6 small pentode on *plate curves* for a fixed screen and filament voltage. Control grid voltage curves are marked as  $E_{Cl}$ , marked negative relative to cathode.

However, with an unbypassed series cathode resistor of 560 Ohms and 185 VDC cathode-plate, the control

grid input voltage versus plate voltage can be taken as:

| Eg-k | Ip,mA | Ep  | Ip+Isc, mA | Ek-grd | <u>Eg-grd</u> |

|------|-------|-----|------------|--------|---------------|

| 0    | 35    | 40  | 37.5       | 21.0   | +21.0         |

| -3   | 29.5  | 68  | 31.5       | 17.6   | +14.6         |

| -6   | 22    | 104 | 24.5       | 13.7   | +7.7          |

| -9   | 15    | 135 | 17.5       | 9.8    | -0.8          |

| -12  | 9     | 170 | 11.5       | 6.4    | -5.6          |

| -15  | 4.5   | 192 | 7.0        | 3.9    | -11.1         |

| -18  | 2.2   | 205 | 4.7        | 2.6    | -15.4         |

Taking the -3 V and -15 V grid-cathode rows, the plate-screen current is 31.7 and 7.0 mA and plate current is 192 and 68 V. Grid to ground voltages are +14.6 and -11.1 which would be the peak to peak value of audio input; RMS audio input is approximately 9.09 VAC. Plate voltage change is 124 V peak-to-peak and plate current change is 25 mA peak-to-peak. Those translate to 17.3 VAC

RMS and 8.7 mA RMS for an approximate plate output of 151 mW. Gain of the audio output driver circuit is then 124 / 17.3 = 7.17 times or 17.1 db in voltage.

If the cathode resistor (for self-bias) is included, the voltage gain would be 124 / 12 = 10.3 times although the distortion would be more pronounced.

# **Resistance-Coupled Amplifier Charts**

About the start of WWII appeared *Resistance-Coupled Amplifier Charts*, primarily to reduce the need for bulky and heavy (and expensive) transformers for audio coupling. Such charts, primarily for low-power audio stages, could be taken verbatim for all values. Those needed only resistors and capacitors. Such charts were available for most low-power audio stages and used in various designs to eliminate lower-power audio coupling transformers.

# **Transmitting Applications**

# General

Receivers could be built from negative-grid-bias circuits almost entirely (except for certain musical-instrument audio stages). Transmitters required an intermix of negative grid bias with high power amplifiers needing zero bias voltage or a form of near-zero-bias where the tube control grids drew current. Most of such higher-power RF amplifiers would have the grid swinging into the positive grid-to-cathode potential over part of a stages RF cycle.

# The First of the Amplifier Classes

These were three types, **A**, **B**, and **C**. Type A was considered for most low-power circuits, the control grid always in negative potential relative to the cathode. Type B had a zero-bias grid and, with a push-pull arrangement, was generally considered a *linear amplifier*. For half of a signal input cycle, the grid would draw current as it went positive, then nearly cut off on the other half of a signal input. Together in a push-pull arrangement they would be considered *linear*.

Type C had varying grid bias voltages, usually with the grid being at a negative potential relative to the cathode but would be swinging into the positive grid-cathode region during part of the RF cycle of power input. Class C amplifiers were the *brutes* capable of delivering Watts and KiloWatts (sometimes even Megawatts) of power into an antenna for transmitting.

A problem with Classes B and C was that they both delivered *harmonics* of the lowerpowered RF cycle input. This was because of the distortion introduced when the control grid swung positive relative to the cathode; the tubes themselves lost their linearity due to loading the driving stage.<sup>8</sup> This was both good and bad. It was good for use as a *multiplier* stage to output a deliberate harmonic. It was bad for a power amplifier that should have output the fundamental. Fortunately,

<sup>&</sup>lt;sup>8</sup> It should be emphasized that the control grid is normally a very high impedance in Class A due to its negative potential relative to its cathode. Once it starts to draw current the high impedance is lost.

L-C tuned circuits (relatively narrow-band) could select the proper harmonics for either case.

Later there were two in-between classes called  $AB_1$  and  $AB_2$ , where the bias point was very close to Class A but not quite on-the-money. Those were developed for the *high-fidelity* hobbyist who craved more audio speaker power with minimal distortion.

With the oncoming transistor stages there were more *classes* added, such as **D**, **E**, and **F**, all three using forms of pulse-width relative to power amplifier output along with some averaging filtering of generated harmonic powers. There were some types of tube circuits tried with pulse-width modulation but those were generally dropped quickly when power transistors were available.

#### **Class B and C Input Loading**

Once rather popular with amateur radio afficionados, those have been dropped from new designs. Design details are rather sketchy in those regards and much of it has become old and, now, unused for new designs. It is popular in newer designs to use low-power Class A biased circuits for driving the final amplifiers in HF equipment. If anything is done for non-linear biasing, it is with passive circuitry such as diode mixers to change frequency by heterodyning.<sup>9</sup>

Those who wish to use tube circuits for multiplication are free to consult old ARRL texts for more information on multiplying to achieve harmonic band-spreads.

# **Video Amplification**

#### General

This is more concerned with the output or plate circuit of tubes. All vacuum tubes have some finite plate output capacity. That normally limits the upper frequency region due to excessive capacitive reactance loading of a load impedance. The point here is to lower the resistive part of a load impedance until the capacitive reactance is (somewhat) dwarfed-out by the lower resistive impedance. Unfortunately, that also lowers a video amplifier's stage gain, requiring more of them to be added to a design and thus increasing the production cost of video receivers.

#### **Operating With Only R and C (and some L) in the Plate Circuit**

A lot of old papers and application notes have been written and published on video amplification, to extend the upper frequency bandwidth using vacuum tubes. Nearly all of those are now obsolete due to lower load impedances possible with solid-state circuits.

As an example, suppose you have a load resistance of 100 KOhms but the combined tube plate, socket, wiring capacity is 15 pFd. The frequency where the total capacity is equal to 100 KOhms is about 106 KHz. Voltage gain at 106 KHz is about at half of the DC value. Dropping the

<sup>&</sup>lt;sup>9</sup> It was once popular to assign amateur radio bands in multiples of harmonics to take advantage of the tube circuit multiplication. Original HF bands for amateur radio were 3.5 to 7.0 to 14 to 28 MHz, each band jump being a second harmonic of the next lower one. With successive World Radio Conferences newer HF bands were allocated so that there were no longer the emphasis on harmonics.

load resistance to 10 KOhms will drop the voltage gain to about one-tenth of what it was at 100 K resistance but the high-frequency end is now about 10 times higher, roughly 1 MHz.

A solution is to use a tube with higher  $g_M$ , higher plate current, and lower load impedance. This will not solve the low-frequency response but it does provide a wider bandwidth. Lowfrequency response is still following the  $g_M \times R_L$  so you might need two video amplifiers in series for a wide bandwidth. An alternative is to use a series inductance with the load resistance to make up for the total load resistance drop due to total output capacity. There are several papers on such load impedance adjustment involving R, C, and L. I won't go into such things since those haven't been used in new designs for over three decades but they are available and can be found.

The old Tektronix 540 series oscilloscopes were built with the final CRT vertical deflection plate coming from a multi-stage, push-pull (differential) *distributed delay line* load impedance. Those would have the total output capacitance as part of the delay line distributed capacity and could carry the higher-frequency up to better than 25 MHz. This seemed to be the ultimate in repeatable, production units including military hardware in the era of the 1950s.

Vacuum tube voltage amplifiers are limited in upper frequency response by another phenomenon: *Electron transit time effects.* That is, it takes a longer time for changes in tube electron flow to get from cathode to plate than in free space. The choice there is to make tubes physically with as little space between cathode-grid-plate as possible. Unfortunately, the limitation is roughly about 2 GHz at the maximum bandwidth.

# **Tubes for Microwave Transmission**

# Magnetrons

These essential RF power oscillators for microwave ovens are basically diodes sitting in an intense magnetic field. They are capable of very high RF peak power happening at around a microSecond (in radar transmitters) or at lower power (for microwave ovens). The combination of the diodes, magnetic field, and a load impedance of a cavity resonator will determine the operating frequency. Magnetrons can operate up to about 25 GHz but the microwave ovens are at about 2 GHz due to the frequency allocated to the ISM or Industrial-Scientific-Medical band.

# Klystrons

Smaller cousins of Magnetrons, Klystrons have little external magnetic field and were originally conceived as the Local Oscillator for radar receivers, converting incoming microwave energy down to about 60 MHz band-center. Their internal structure is only slightly more complex than a Magnetron. A typical Klystron of WWII was about the size of an octal-based metal-envelope vacuum tube. After WWII higher-power Klystrons were used for UHF TV transmitter final amplifiers. Those may be several feet in length, dependent on RF power output.

# **Traveling-Wave Amplifier Tubes**

Abbreviated TWT, these are an old design but have about an octave of bandwidth. Their

internal structure resembles a vacuum tube electron flow going through a helix or spiral delay line extending nearly the length of a TWT envelope. TWTs are capable of very wide bandwidth and have low internal noise (relative to other microwave tubes). As of 2010 they are still the transponder group amplifier for communications satellites in orbit.

# **Display and Glow-Discharge Tubes**

# **Cathode-Ray Tubes**

One of the first of the non-amplifying type vacuum tubes built, a CRT is basically a small beam of electrons from an *electron gun* structure that can be focused on a phosphor coating at the faceplate. Deflection of the electron beam can be done electrostatically (as in many older oscillographs) or magnetically (as in most TV receivers). The first of the CRT deflections was electrostatic, done directly from a source since there was a lack of a wideband voltage amplifier. With the advent of lower-cost TV receivers of 10-inch and greater deflection, they were magnetically deflected. Electrostatic deflection was limited to about 7-inch picture sizes.

Original deflection angle was roughly  $\pm 3$  degrees in the beginning, increasing to about  $\pm 45$  degrees with color TV sets. Prior to being outsold by flat-panel TV displays, automatic production machinery made it possible to produce relatively low-cost CRTs and with triple dot-patterns of phosphors for color TV. Deflection at lower angles is proportional to the DC level of electrostatic deflection, hence they could be used as oscillographs at very fast rates.

With most CRTs in-use, the electron beam is constantly increasing in potential along its length. For electrostatic deflection the deflecting plates (a form of anode) may have up to 300 V of DC potential for small CRTs while the magnetic-deflection color TV CRTs may have up to 25 KVDC of its *ultor* or ultimate internal electrode. The ultor is formed from a conductive carbon coating on the inside of the bell or widening of the CRT.

# **Neon Pilot Lamps**

Since before the end of WWII, pilot lamps had been standardized in bases and general sizes. The common pilot lamp (to indicate something was on) was a #47 incandescent, taking 150 mA at 6.3 VAC or VDC. By contrast, the NE-2 neon pilot lamp could do the same job with only a tenth of the electrical power of an incandescent bulb. While those were used in new equipment, they never caught on with industrial designers, despite their lower power demands.<sup>10</sup> Those did lead to a newer, faster, numeric indicator for a new instrument, a frequency counter.

#### Nixies

Originally a trademark of the Burroughs Corporation, a NIXIE was a clear glass enclosure

<sup>&</sup>lt;sup>10</sup> A minor tale: When working at WREX-TV in Rockford, Illinois, the author replaced a number of neon pilot lamps in General Electric studio equipment in 1956. Engineers on day and night shifts did notice that since the older bulbs were rather used. The author was kidded about that for a long while.

containing at least 10 electrodes formed into numeric characters. Energizing just one of the electrodes would light up that one numeric and it would emit a visible glow. Some extra driver circuits could be added between electronic flip-flop counters and a Nixie such that the Nixie would show the state of the count.<sup>11</sup> Those would all be replaced with LED displays or other solid-state types later but a few hobbyists still like the Nixie for things like clock displays.

# **Magic Eyes**

The first *magic eye* tube appeared in the 1930s as a tuning aid for multi-band receivers. Their purpose was to show when a station was tuned in exactly on-frequency, or at least within the passband of IF stages. A few were used in WWII military transmitters are very rough current indicators. Those worked like very small CRTs and were bypassed after WWII. Hobbyists saw a resurgence in Magic Eye tubes at the end of the old millennium but that has appeared to lapse.

# **Night-Observation Devices**

The first *electronic eye*, or cadmium-sulfide junction, is older than vacuum tubes. Those increased in sensitivity by adding internal electron-multiplier stages in a vacuum, were used in electro-optical instruments. By the time that solid-state electronics had developed greater sensitivity, a few tube makers tried for ultimate sensitivity in the *NOD* or Night Observation Device, sometimes called a *Starlight Scope*.

# **Digital Devices**

# **The First Computer Circuits**

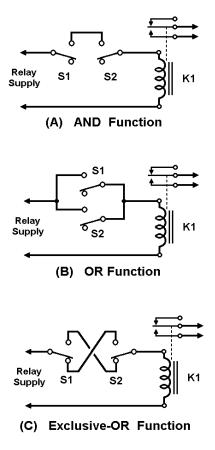

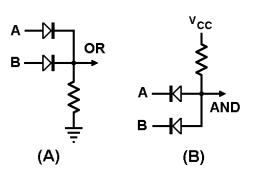

Vacuum tubes were not very suited to digital devices in computing. At best, an analog computer was available as a kit from Heath Company.<sup>12</sup> Analog computation rather regressed in favor of the more reliable solid-state computation at the appearance of this kit. The first digital computer circuits used a combination of devices: Diodes for AND and OR gates followed by level shifting triodes to increase their outputs or to interface with the outside world. At best, tube digital circuits could reach 10 MHz counting rates (Hewlett-Packard model 524 series), taking a lot of electrical power to do so.

# Non-Linear Devices as a Group

<sup>&</sup>lt;sup>11</sup> Nixies did not come on the market immediately, were preceded by edge-lit Lucite panels to indicate numerics in the 1950s. A groove in a Lucite panel would cause an incandescent bulb (off of the edge of a panel) to illuminate the numeric carved into the Lucite. Any character could be displayed in that manner. After Burroughs came out with the Nixie, a number of different makers had their own versions, including a Great Britain version that was bi-quinary and easier to drive than single-electrode standard Nixie types. Previous to the Nixie, frequency counters used neon bulbs in a *vertical row* called a *thermometer display* (Hewlett-Packard 524A and 524B).

<sup>&</sup>lt;sup>12</sup> It only lasted a couple of years in Heathkit catalogs.

The 1960s saw the greatest number of non-linear vacuum tube devices, mostly as test equipment and in video processing. Potentials in tube circuits were rather great and stray reactances limited speed. Some test equipment used special tubes (developed for the purpose) for (at the time) fast pulse forming and handling. The 1960s were also the date of introduction of practical transistor junction circuits which would take over the electronics world from then on. But, there were some oddities insofar as tubes were concerned.

# **Radiosondes (Weather Balloons)**

A type of tube was especially designed to be made cheap and (essentially) thrown away on use. This was the *pencil triode* intended for weather balloons. The pencil triode was crimped into a sheet metal housing which was also its resonator and would become a UHF oscillator. Together with a single standard tube (later transistor) as a variable PRF oscillator connected to a variety of equally-cheap sensors, it would form the heart of weather balloons in the 1950s and 1960s. On the order of a half-million per year were dispatched in that time. Those formed the first of the true weather pattern mapping efforts of the world. Once into the 1970s their use would diminish as special geostationary satellites would do the mapping.

Using a one-shot battery, the radiosondes would be tracked by the receiver part of an converted radar set for positioning. As they rose under their largish balloon filled with helium, an aneroid barometer would act as a switch to both indicate altitude and to connect various sensors. They were designed for minimum damage should they be struck by another aircraft.

# **Small-Boat Limited-Range Radar**

Those were built from some radiosondes, basically the pencil triodes used for oscillators. Their *radomes* would see later use as housings for recreational vehicle TV and FM antennas.<sup>13</sup> Their range was limited due to lower peak power but was enough to navigate through inland harbors and other waterways.

# **Other Special Tube Uses**

# Nuvistor

These were a miniature metal-glass envelope type of vacuum tube, most of them being triodes. They can also be thought of as a *last gasp* of the vacuum tube industry during the latter part of the 1960s against the semiconductor. Their major attribute was being small yet still had pins for replacement. It is very difficult to get a socket for a Nuvistor by the year 2010. Without a socket there isn't much need to include a Nuvistor in a new design, especially in a hobby project.

# **12 VDC Plate Supply Tubes**

<sup>&</sup>lt;sup>13</sup> Circular flat plastic housings having low height.

Another *last gasp* by the tube makers, these followed the Nuvistors. While their envelopes were mainly those of 7- and 9-pin all-glass types, their main attribute was a rethinking of the internal electron flow optimized for 12 VDC plate supplies. Many different types were made for the automobile receiver market but that bottomed out for tubes also. These do work, though.

# More than One Type of Tube in the Same Envelope

These must have been the very last of the *last gasp* attempts to make inroads into the consumer electronics industry via tubes. Mainly they were a combining of two- and three separate functions, all isolated except for filaments. These were also short-lived on the industry market. Again, their separate tube sections did work well but, by the 1970 time frame, they were too late in reaching the market.

What the designers could not do is to make them replaceable easily without a socket. With so many functions and more pins than standard, they could not be cost-competitive with transistors using PCB mounting. Sockets for these tube types are mostly made of unobtainium by 2010.

# 5000. 6000 Series Tubes for Demanding Applications

These were improved versions of standard, registered types intended for military, mobile radio, or other harsh environments requiring greater filament life and/or more stringent *typical* curves of internal characteristics. In most cases the socket pin-outs are equal to their original types so replacement is not a problem. In general, such tube architectures were replaced (eventually) by their smaller solid-state counterparts.

# A General View of Envelopes and Support Structures

# **Envelopes**

In the USA at least, the first vacuum tubes were a hit-and-miss affair, being largely all-glass and having connections by wires. Those solidified to having bases which would plug into sockets. The first such bases were 4-pin affairs. With the internal structures including extra grids, either a plate or grid cap was placed on the opposite end of the glass tubing from the base. Eventually those were replaced with a more-standard 8-pin base called an *octal base*. Industrial standardization had begun. Interior structures tended to be largely spot-welded with sheet mica or ceramic insulators, vacuum retained with external connections going through metal-in-glass seals to retain a vacuum.

In the 1930s the octal-based tubes got metal envelopes, partly for shielding, partly for slightlybetter heat dissipation. Glass envelopes were still favored among tube makers. By the end of the 1930s a newer envelope was developed entirely from glass. Base pins tended to remain being metal within glass, usually for 7-pin connections going to small sockets. Those were called 7-pin miniature tubes. Also developed were some non-standard all-glass envelopes fitted for more direct connections, called *acorn* tubes for their resemblance to the seed. The 7-pin bases were expanded to 9 pins to handle dual triodes, isolated except for the common filament connections. After WWII the all-glass envelope was expanded to include multiple tube structures within one envelope. Manufacturers in the 1930s also developed ceramic-metal seals, coming to fruition after the 1930s with the *lighthouse* tubes for low microwaves and UHF. Lighthouse shaped tubes had very little spacing between internal tube elements to reduce the electron transit time effects. Lighthouse shaped tubes were of two types: Direct with the plate being at the narrow end of the lighthouse shape followed by the plate having the larger end with cooling fins added for heat dissipation.

RF power output tubes tended to be more conservative, most older designs having robust allglass envelopes with newer types having ceramic-metal seals for the post-WWII market. The latter would survive for the longer-lived RF power amplifiers, from triodes to Klystrons for TV transmitters to TWTs for microwave work. Magnetrons tended to be large due to their (usual) integral magnet although they were essentially multiple diodes internally. Pencil triodes had the general diameter of a common lead pencil with the grid brought out to a wider disc. Pencil triodes would be crimped with a sheet-metal double cavity resonator for fixed-frequency radiosondes.

#### **Oddities**

The Nuvistor was one of the last of the post-WWII designs, intended as a replacement of solidstate transistors. Nuvistors were used in new designs for about a decade but replacement was difficult due to very small base pin-outs. The military got into the act with 8-pin subminiature tubes right after WWII for portable radios, subminiatures being half the diameter of the miniature all-glass envelope type.. The AN/PRC-6 handheld transceiver used a dozen 8-pin subminiature tubes plus one 7-pin miniature for the transmitter output tube. The subminiature type tube tended to disappear by the time of the Vietnam War and the all-solid-state (except for transmitter power output) AN/PRC-25.<sup>14</sup> One of the busts of military development was the one-soldier, one-radio type of *squad radio* at the start of the Vietnam War which had to be re-engineered to become practical. Even so, its early development time proved it a failure.

Photomultiplier tubes used in optical instruments were revised for Night Observation Devices and eventually took over most of the extremely low-light-level of illumination for night warfare. Those came out first as all-glass, then changed to glass-metal envelopes, eventually to all-metal and ceramic envelopes. Display CRTs were generally all-glass envelopes although a combination glass and metal envelope was tried, both for consumer and military-industrial electronics.<sup>15</sup>

In general, when confronted with new developments, established manufacturing tends to be somewhat conservative in trying out older constructions. The time of the vacuum tube was over by the entrance into the new millennium. The only life left for them was for replacement.

#### The End Result of Vacuum Tubes in the New Millennium

Except for specialty areas of NODs, communications satellite transponder relays, plus the

<sup>&</sup>lt;sup>14</sup> The AN/PRC-77 had the same case and controls as the -25 except the transmitter power output stage used a solid-state transistor in place of the tube. Both the -25 and -77 used frequency synthesis with channelized tuning from the front panel.

<sup>&</sup>lt;sup>15</sup> As CRTs got larger there was an apparent lack of attention to handling among some manufacturers, especially if the large CRT was already evacuated, hence the shift to a nearly-all-metal envelope structure. There is no other reason for an envelope to be made of metal.

radar or microwave oven output stages, there is no call for vacuum tubes in consumer electronics designs. There is a nebulous market in the niche for guitar amplifiers. That was bolstered by the ability certain types of audio distortion produced by tube amplifiers as opposed to semi-conductor amplifiers, both when over-driven. Vacuum tubes are relatively simple devices and they did usher in the wealth of electronics that dominates our senses now. But, they have a number of faults.

Basically, vacuum tubes are troubled by filament-heater burn-out. Although efforts were made in the 1970s to improve filament life, that failure is still the driving force for replacement. There are limitations to the size of electronics systems from that single failure rate. A secondary failure was losing the vacuum within due to leaks in various places of a single tube.

Size and potentials within tubes are a second limiting factor. From the laws of physics, tubes require a relatively high voltage for its electrodes. Add to that the factor that electrons will move only from cathode to plate through plate-current-current controlling grids. Amateurs tend to be conservative in naming their HF radios by old tube type numbers, largely from nostalgia and familiarity with such old type IDs. Thousands of different tube types were designed between 1910 and about 1980, all with different characteristics and uses. All were useful but the electronics market has dropped out in favor of just a few by 2010, evidenced by distributor catalogs.

The only thing left for vacuum tubes in most hobbyist projects is for replacement or reconstruction. Even so, many tube types have tended to disappear.

# Chapter 21

# **Semiconductor Basic Applications**

A guide to semiconductor active device applications, this Chapter has an overall look at then as the devices of choice used for nearly all electronics in this new millennium.

# **A Bit of History**

The first research into semiconductor technology might be taken as roughly a quarter-century before the first demonstration of radio as a means of communication. In 1874, Leipzig, Germany, Karl Ferdinand Braun published a paper on what would eventually become the first devices to enable rectification of an RF signal.

By 1879, Edwin Hall of Johns Hopkins University published a paper noting that the direction of current (and resulting Ohm's Law of Resistance) changed according to an external magnetic field. While nothing much was done about this discovery then, it became noteworthy in the next century as *Hall Effect Sensors* as special versions of semiconductors today.

In 1938 William Shockley, at Bell Telephone Laboratories, was trying out his *new idea*, to build a three-terminal device which might be able to amplify electrical signals using only semiconductor material. Not much was done during World War II days, but after, with partners Walter Brattain and John Bardeen, they made it work. Just before Christmas of 1947 the trio presented the first point-contact transistor to Bell Labs personnel and a patent for their invention started in process. That patent was granted by the middle of 1948.

At about the same time, but in 1943 in Paris, France, for a Westinghouse division there, Herbert Matare' and Heinrich Walker came out with a point-contact transistor they called a *transitron*. In 1948 they presented a more-polished version, presumably good for sales.<sup>1</sup> Not too long after, James M. Early, working at Bell Labs, came up with the *Early Effect* to explain the common transistor voltage-current curve origins.

The whole point of using dopants was to create a *free* electron or the *lack* of a free electron in the semiconductor material. An excess of electrons caused N-type junctions; the lack of a free electron caused P-type junctions. Combined with the otherwise-uninteresting semiconductor material of germanium or silicon, it now resulted in the astonishing action of controlling electron flow. Note that, by itself, germanium and silicon are only so-so insulators and so-so conductors of electron flow, hence the name of **semi**conductors. Yes, crystalline carbon can be made into transistor junctions and has been done in the laboratory but the cost of fabrication was too far out of commercial reach to make it possible. Crystalline carbon is, of course, diamond.

What hindered these beginners in semiconductors was metallurgical instruments. Silicon has about  $5 \times 10^{22}$  atoms per cubic centimeter. A dopant of phosphorus (N-type) or boron (P-type)

<sup>&</sup>lt;sup>1</sup> EDN magazine website blog at the beginning of February 2011 entitled *Who Invented Something Depends on Your Definition of "Something."*

can be done with just 5 x  $10^{15}$  atoms per cubic centimeter. The difference is 1 x  $10^7$  atoms, slightly less than the normal impurity from all causes in both germanium or silicon.<sup>2</sup> Before some new things were able to be investigated, metallurgical impurity measurements had to be much improved!

It should be noted here that, once fixed into a dopant area, the dopant will *remain fixed*. It will not move until something catastrophic happens to a semiconductor.

# Hole Flow in P-Type

The concept of having a *nothing* (lack of an electron) moving in a fixed crystalline structure bothers the author. If you can accept that, fine. We either have *something* (an electron) moving about in doped material or we have *other* electrons moving about to *leave a hole* there.

# **Temperature Effects**

Movement of extra electrons (or lack of them) occurs mainly in the temperature range of about  $-60^{\circ}$  C to about  $180^{\circ}$  C. Below  $-60^{\circ}$  C there is almost no reorganization movement but by about  $+200^{\circ}$  C both silicon and germanium start to become reasonable conductors.

# DIODES

Take a rod of silicon and dope one end to P-type and the other end to N-type. What you get is an electron flow from N-type to P-type, but almost nothing in the opposite direction. This is the only similarity between tubes and semiconductors; one-direction conduction. There are some particular specifications that *must* be obeyed for any diode, from power rectifiers to small-signal types:

- 1. Average Forward Current: This determines the in-circuit heating effect with a forward current drop of about 0.7 VDC (silicon) to about 0.3 VDC (germanium).

- 2. Breakdown Voltage: Reversed polarity withstanding voltage. This is absolute.<sup>3</sup>

- 3. **Maximum Forward Current:** Applies largely to rectifier types at turn-on, initial surge to charge up filter capacitors. Usually given with a time scale for maximum current.

- 4. **Duty Cycle**, primarily for high-current diodes. Relates to power dissipation in forward conduction.

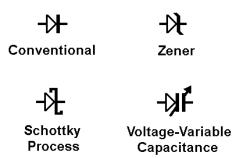

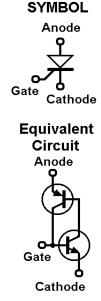

Chapters 22 and 31 cover power supplies. Chapter NN has specific supply information for 100 VDC regulators. Ordinary diode use is scattered throughout after this Chapter. What follows here is a brief description of some diodes for special applications from DC through VHF which are also used.

# **Voltage-Variable Capacitance Diodes**

These are diodes designed to be used in *reverse* polarity such that junction capacitance is

<sup>&</sup>lt;sup>2</sup> It is a bit like saying a pinch of salt in a boxcar full of sugar... or better than 10 parts per million.

<sup>&</sup>lt;sup>3</sup> Zener diodes are designed to work *at their breakdown voltage*. This is the main exception from other diode types. A forward-biased zener diode is simply an ordinary diode.

inversely proportional to reverse voltage. They can be used the same as old mechanical variable capacitors for RF circuit tuning.

# **Zener Diodes**

Again, these are used in **reverse polarity** for a specific voltage breakdown fabricated into the diode. Their use is mainly as shunt-voltage regulators for a voltage reference. They are quite stable within a certain specified zener current range. For the least noise across the reversed junction, a more complex *band-gap reference* is used, consisting of two or more transistors. Depending on the type, a forward-blocking current diode may be added to prevent conduction in the normal direction, limiting zener effect to the breakdown region.

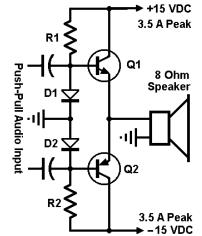

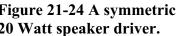

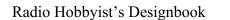

Figure 21-1 Diode Symbology

#### **Schottky Diodes**

These are diodes with junctions made in the *Schottky process*. That results in a lower forward-bias voltage that can extend almost to zero current. They are excellent for low supply voltage rails and specialized applications such as switching regulators. Note that the *Schottky process* can be done with digital circuitry to cut idling current almost to extinction.

# TRANSISTORS

N - Type

#### General

These are, as of 2013, three principle types: Bipolar-Junction, Junction Field Effect, and CMOS Field-Effect. In general they are all equal to vacuum tube triodes. The difference from tubes is that PNP and NPN junctions can be reversed; whereas vacuum tubes always require electron flow from cathode to anode. *Great* designer convenience.

# Junction FET Transistor

P - Type

#### **Bipolar Transistors**

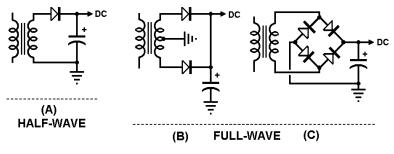

The name refers to the direction of electron flow within. An **NPN** transistor has the **emitter** connected to the lesser

Figure 21-2 Symbology of common transistors. Note the arrows to mark type/polarity.

potential and electrons will flow from **emitter** to the **collector**. The **base** electrode controls this flow relative to the **emitter** potential and, for an NPN transistor will have its **base** acting as a diode

Radio Hobbyists Designbook

**Bipolar Junction**

Transistor

connected to the emitter. The collector-to-emitter equivalent circuit will be like a reversed-biased diode, the cathode at the emitter and anode at the collector.

A **PNP** transistor is the same except the electron flow is *reversed*. Electron current flows from collector to emitter and from base to emitter in a PNP, opposite to that of an NPN. The base-to-emitter junction will always behave as a forward-biased diode for either PNP or NPN. Only the direction of current will signify the real differences.

Note the *arrow* in Figure 21-2. For BJTs it follows the old *Franklin current flow*, opposite that of real electron flow. For FETs it is more like *electron flow*. JFET and CMOS symbolism came later.<sup>4</sup>

# **CIRCUIT APPLICATIONS, Basics**

# General

This begins with low signal level amplification, shifts to not-quite-so-linear high-level amplification, and finally to On-Off, non-linear digital circuits. It should be noted strongly that gain and impedance formulas given in here are *only approximate* for *first-guess* gains and impedances. Given the number of free circuit simulation programs now available, final gain and impedance numbers can be found more accurately through computer simulation.<sup>5</sup>

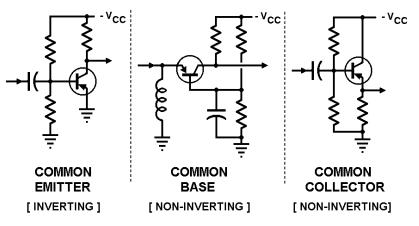

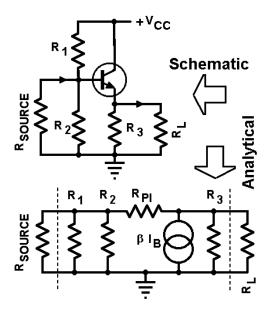

# **Three Ways to Connect Transistors**

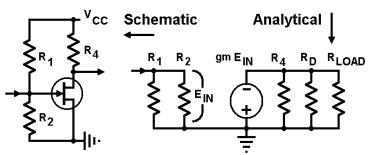

Figure 21-3 shows the basic configurations for PNP PNP BJTs. Output has a generic resistive load resistance, from collector to supply for Common-Emitter and Common-Base while it is from emitter to ground for C o m m o n - C o l l e c t o r. Remaining resistors are to set the *bias* for determining collector current in a quiescent condition.

Figure 21-3 Three ways to connect a transistor.

This applies to Ntype FETs, substituting Gate

for Base, Source for Emitter, and Drain for Collector. P-type FETs and PNPs require a *negative* voltage polarity. Note that Common-Base has an inductor to provide a DC return for the emitter.

<sup>&</sup>lt;sup>4</sup> That may have resulted from higher-rank engineering types having to master old electronics texts where the old (reversed) *Franklin current flow* was used. [Speculation by the author]

<sup>&</sup>lt;sup>5</sup> Primarily *LTSpice* from Linear Technology and *TINA* from Texas Instruments as of 2013. Free downloads and upgrades. There are variations in semiconductor specifications from manufacturers and those can be simulated fairly easily on a PC.

That return can be an inductor in the output of an L-C filter.

# **DC Biasing**

# **Determining the Operating Point**

This uses the *Load Line* method, very similar to use with vacuum tubes, to determine the DC current demand. On a set of *collector curves*, place a *Load Line Slope* such that it intersects one of the Base current lines. The Load Line *Slope* has an angle of the *load resistance*. Given a resistance of 1000 Ohms with 16 VDC for Vcc, maximum current is 16 mA. The slope will go from

maximum current at zero collector current to maximum supply voltage with no collector current. An example set of *curves* with a *load line (dashed line)* is shown in Figure 21-4.

An **Operating Point** is chosen **on** the load line for a no-signal axis. In this example it is about 8 mA. At that *Operating Point*, collector-to-emitter voltage would be about 8 VDC. At the same time the base current can be found, very roughly at about 155  $\mu$ A.<sup>6</sup> For this example, call it 160  $\mu$ A.

In order to set the Operating Point, a transistor must be **biased** externally so as to make the base current close to 160  $\mu$ A. This can be done simply with two resistors which **waste** anywhere from about 4 to 10 times the base current. The reason for such *waste* is to do some stabilization of base biasing for both  $\beta$  variations and for temperature. Note that resistors are generally less sensitive to thermal effects.

Figure 21-4 A fictitious set of *collector current curves* as an example. The *load line* may move anywhere horizontally but not vertically.

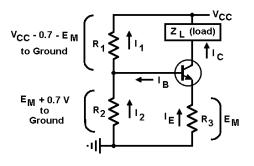

# **Simple Base Biasing**

DC circuit given in Figure 21-5, formulas are simple:

<sup>&</sup>lt;sup>6</sup> It is difficult to exactly measure base current from a collector current curve set. Curves are all *typical* but each transistor has a variation of Beta at DC and at an operating frequency. A datasheet for a transistor will show some other manufacturing percentage variations to confound the calculation problem as well as transistor operating temperature that also changes the forward-biased base-emitter diode portion of the transistor junction.

$$I2 = \frac{0.7}{k \cdot I_B} \qquad R2 = \frac{0.7}{k \cdot I_B} \qquad R1 = \frac{R2 \cdot (Vcc - 0.7)}{I_B \cdot R2 + 0.7}$$

k is approximated to anywhere from 4 to 10

Making R2 = 1 KOhm and then R1 = 18 KOhm would make  $I_1 = 850 \ \mu A$  and  $I_2 = 700 \ \mu A$ .  $I_B$  would then be the difference or 150 µA. That is fairly close to a correct Operating Point.

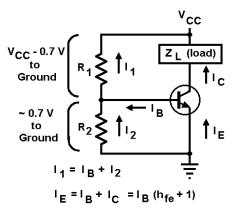

#### Self-Bias With a Series Emitter Resistor

Figure 21-6 Self-bias circuit.

fairly easy on a handheld calculator. The approximate formulas:<sup>7</sup>

$$E_M = R3 \cdot I_B \cdot (\beta + 1)$$

$I_2 = \frac{(E_M + 0.7)}{R2}$   $E1 = Vcc - E_M - 0.7$   $R1 = \frac{E1}{(I_B + I_2)}$

shows

Voltage across the emitter resistor, R3, can be picked to (initially) be about 10 to 15% of the load resistance, RL. Choosing 150 Ohms would make Em about 1.224 VDC with 8 mA Ic and a ß of 50. Adding the base-emitter voltage drop of 0.7 VDC makes the total of 1.924 VDC. Choosing R2 to be about 3.9 KOhms, I2 would be 493  $\mu$ A. Summation of I<sub>2</sub> and I<sub>B</sub> equals 653  $\mu$ A. Finally, with a 22 KOhm R1 (rather than a calculated 21.54 K) the circuit settles in approximately correct.

Figure 21-6

а

#### Variations for FETs

While Figure 21-3 shows BJTs, the Bias circuits will apply to FETs. Only the electrode connections change names. Depending on the schematic form, resistors external to the transistor will have the same connections. As to configuration names, the following is worthy of note:

| BJTs                           | FETs         |  |  |

|--------------------------------|--------------|--|--|

| Common-Emitter = Common-Source |              |  |  |

| Common-Base = Common-Gate      |              |  |  |

| Common-Collector =             | Common-Drain |  |  |

<sup>&</sup>lt;sup>7</sup> These simple formulas are *not exact.* For an exceedingly exact group, see Agilent Application Note 1293 A Comparison of Various Bipolar Transistor Biasing Circuits, document 5988-6173, 22 January 2003. Available free over the Internet at www.agilent.com. While those are very nice, the number of (sometimes) hidden variables can befuddle their exactness for hobbyists. The best way to check your bias circuit is to load it into LTSpice and do a test for currents and voltages. That comes as close to reality as tens of thousands of dollars of fine equipment.

third Figure 21-5 Simple bias circuit. resistor in series

This begins by picking Em first, then I2 for a value of about 4 to 10 times Ib, finally R1, all within a manufacturing-tolerance resistor value limits. This is not a super-formula method but it is simpler and may be done

with the emitter. At DC this provides a bit of negative feedback by trying to stabilize the base current. Α problem is that there is the voltage across R3 which must be factored into the Simple bias circuit of Figure 21-5.

Note: FET Gates have very low current levels, hence FET Bias resistors can be selected as simple voltage dividers, ignoring Gate current.

# Large- and Medium-Signal Gains and Impedances

This can be approximated directly from Load Lines but is quicker and easier to do with a SPICE program. A feature of both LTSpice and TINA (both free programs for PCs) is the ability to discern the level of harmonic generation from non-linearity. The *magnitude* of input impedance can use a single series resistor, adjusted in value until the input voltage is half that of the voltage source. Input resistance is then equal in magnitude to the series resistor value. Approximately the same simple technique can be used for output impedance, varying the final load resistance until the output voltage is about half of the no-load-resistance voltage.

Note that the *magnitude* is found, not the explicit (so-called perfect) value. There will be some transistor and other wiring capacitance in parallel which will reduce the *magnitude*. That can also be modeled but the amount of effort increases by roughly the cube over using a simple resistor in series method.

# **Small-Signal Analysis**

#### General

*Small-Signal* levels are those measured in milliVolts or microVolts peak-to-peak. What is lovely about a PC analysis and design program is that it doesn't care about the absolute levels. To such a program it is merely a number entered for amplitude of a source generator. This makes it ideal for input stages of a receiver as an example. Harmonic content can still be calculated so it is possible to predict things like mixer spurious products or the interference from same. Such features are virtual spectrum analyzers on the screen.

In order to get a circuit model requires a basic circuit. What is given following are the simple *approximation* formulas for Gains and Impedances. Individual component values can be changed to fit the overall circuit. Having a circuit model allows fairly simple component changes to see their effect on overall performance.<sup>8</sup> You will **NEED** a model for accurate system answers.

In the Bias of BJTs the simpler  $R_{PI}$  value comes up.<sup>9</sup> This approximate value is based on the Base-Emitter current derived from the Operating Point. One takes the Base voltage relative to the Emitter and divides that by the Base current. In the BJT example given previously, the Base voltage to ground was 1.924 VDC. Dividing that by 160  $\mu$ A Base current yields 12.025 KOhms.

The double vertical bars denote *parallel connections*. For resistors the total parallel value is the reciprocal of the sum of all individual reciprocals. On a scientific calculator with a 1/x function key, that is very quick and easy to do.

<sup>&</sup>lt;sup>8</sup> That cannot be stated enough. Computer-aided circuit analysis came into wide use in the 1970s and has grown ever since. It is *ideal* for the hobbyist...an unlimited number of parts which can be changed easily in order to optimize a circuit. The only problem is the learning curve needed to use such a program.

<sup>&</sup>lt;sup>9</sup> That value is pronounced *R-pi*. That name is unusual in that the symbol of *pi* was not used, rather to spell it as *pi* to avoid conflict with other variables given here and later.

#### **Small-Signal Frequency**

For resistive loads, the initial frequency is taken to be *mid-band*. This will be about 1 KHz for audio circuits. For *tuned* loads, such as parallel-tuned L-C circuits or filters, the initial frequency would be in the *center of the passband*.

There are many different frequency-shaping effects with most circuits.<sup>10</sup> For initial calculations one can assume that coupling capacitors, emitter bypass capacitors, and supply rail filtering become short-circuits at this initial gain and impedance calculation. Once this initial calculation is done, it becomes the baseline for *other frequency* gain reduction and impedance variation.

# **Small-Signal Levels and Linearity**

At input levels of  $100 \,\mu\text{V}$  to  $10 \,\text{mV}$  peak-to-peak the amount of distortion is about the same as if input levels 100 times higher. There are ways of reducing non-linearity; op-amps are the classic case for this. *Negative feedback* is the general way to reduce distortion, but at the expense of lesser voltage gain as compared to a circuit without such negative feedback. Using a series Emitter (or Source) resistor without any parallel bypass capacitor is the classic case.

Once a circuit is modeled with a PC program, the PC analysis program will have a form of *Fourier Coefficient* calculator built-in. This will show both the harmonic content and allow a quick calculation of *Total Harmonic Distortion*.

# **APPROXIMATE Small-Scale GAINS, IMPEDANCES**

# General

These all assume the *Load* is *resistive*. For a reactive Load, use the *magnitude* of impedance as if it were a resistance at that mid-band-frequency.  $R_{PI}$  is the DC bias into the Base as mentioned.

# **Common-Emitter, no Emitter Resistor**

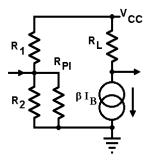

Voltage Gain  $= \frac{\beta \cdot R_L}{R_{PI}}$ Current Gain ~  $\beta$ Input Impedance  $\approx R_{PI} \parallel R1 \parallel R2$ Output Impedance  $\approx R_L$

Figure 21-7 Model of Common-Emitter, no series resistor.

<sup>&</sup>lt;sup>10</sup> There are enough variations to fill another book. For hobbyist work, it is quicker to approximate on the mid-band frequency, then model it on a PC program and refine the upper and lower frequencies that way. This doesn't change the Operating Point (set at DC) and the mid-band frequency characteristics are good enough to yield an overall *Gain* **Budget** for a hobby system.

# **Common-Emitter With Unbypassed Series Emitter Resistance**

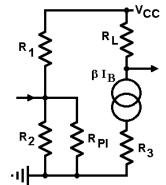

The analytical schematic (Figure 21-8) is the same as Figure 21-7 except it has a series resistance in the Emitter lead, R3. This requires a change in the Operating Point as well as the values of R1 and R2. As a result of R3, the voltage gain drops and the input resistance increases. Collector load is assumed to be the *parallel* of  $R_L$  and the external (driven stage) input resistance.

Voltage Gain =

$$\frac{\beta \cdot R_L}{R_X} \approx \frac{R_L}{R_3}$$

$R_L = R_L || R_{LOAD} [R_{LOAD} \text{ is Driven Stage}]$

Current Gain

$$R_{I2} = R_I || R_2$$

Input Resistance =  $\beta \left( \frac{R_L}{R_L + R_{LOAD}} \right) \left( \frac{R_{12}}{R_{12} + R_X} \right)$

$$= R_{I2} || R_X \qquad R_X = R_{PI} + (\beta + 1)R_3$$

Figure 21-8 Analytical model of a Common-Emitter *With* a series Emitter resistance, R3.

R3 will reduce the voltage gain. As the input signal goes more positive, the Emitter voltage will also go (slightly less) positive, thus, for the same output voltage, the Base must go more positive than in the case of no series Emitter resistance. There is less loading on the input driver since the input resistance has risen above that of the stage without an R3.

#### **Common-Collector or Emitter Follower**

Voltage Gain =

$$\frac{(\beta + 1) \cdot R_{LL}}{R_{PI} + (\beta + 1) \cdot R_{LL}}$$

Input Resistance =  $R_1 || R_2 || R_{PP}$

Where:

$$R_{LL} = R_3 \parallel R_L$$

and

$$R_{PP} = R_{PI} + (\beta + 1) R_L$$

Output Resistance  $\approx \frac{R_S + R_{LL}}{\beta + 1}$ Where:  $R_S = R_I || R_2 || R_{SOURCE}$

Voltage gain of a Common-Collector is in the normal range of 0.7 to 1.0. Input resistance takes a big jump over a Common-Emitter while output resistance falls. This is commonly used as a non-inverting buffer

Figure 21-9 Schematic, Analytical diagrams of a Common-Collector or *Emitter-Follower*.

such that output voltage tends to *follow the input*, hence the colloquial name of *Emitter-Follower*.

In the circuit of Figure 21-9 note the additions of  $R_{SOURCE}$  and  $R_L$ . This is because of their effect on output voltage. While there is little effect except at low values, it was mathematically impossible to divorce them entirely from these approximations.

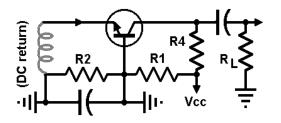

# **Common-Base**

This configuration has very low input resistance, moderate to high output resistance, power gain but the current gain is less than  $\beta$ . It is good for matching a low-Z source to high-Z. Miller Effect is very slight so wideband circuits can go to transition frequency.

Figure 21-10 Common-Base. Shaded inductor represents a DC return for the Emitter to ground. R1, R2 bias for Base are same as for Common-Emitter.

Output Voltage Gain = gm ( $R_4 || R_L$ ) Input Resistance =  $R_{PI} / (\beta+1)$ Output Resistance =  $R_4$ Current Gain ~  $\beta / (\beta+1) = \alpha$ Miller Effect is not present on Grounded-Base.

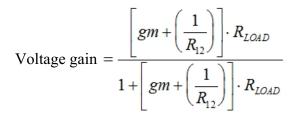

# **Variations For FETs**

Since FET Gates operate more from Gate voltage to ground, the common figure of merit is *transconductance*. *Transconductance* is the small-signal *rate of change of Drain current due to Gate-Source Voltage*. It is abbreviated to *gm* and measured in *mhos* (Ohms inverted) or *Siemens* (the same thing but given a different name). For some clarity, *gm* is used here since it was present in vacuum tube analytical models first.<sup>11</sup>

There is very little Gate current relative to BJTs, enough that Bias resistors can ignore Gate current. There is *no*  $R_{PI}$  in the FET circuit models. Some FET characteristics show some thermal effects with Gate voltage; depending on the specific circuit, those may have to be dealt with.

Gate Bias can be calculated directly as voltages at the Gate. Bias resistor strings can be up to 250 KOhms, thus resembling vacuum tube amplifier stage inputs for Common-Sources.

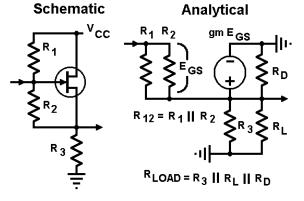

# **Common-Source FET, no Series Source Resistor**

Similar to Figure 21-5, the analytic circuit is shown in Figure 21-11. There is no current connection between input and output.<sup>12</sup> DC Bias voltage, Gate-to-ground, depends on the Operating Point and/or datasheet values.  $R_D$  is equal to reciprocal of gm, mhos of gm turning back to Ohms.

<sup>&</sup>lt;sup>11</sup> See Chapter 20 on vacuum tube basic data for transconductance.

<sup>&</sup>lt;sup>12</sup> There is, but it is confined to Gate-Drain inter-electrode capacitance and affects high-frequency gain.

Output Voltage Gain =  $gm R_L$

$R_{L}^{\prime} = R_{4} \mid\mid R_{D} \mid\mid R_{LOAD}$

Input Resistance =  $R_1 \parallel R_2$

Output Resistance =  $R_4 \parallel R_D$

This is a fairly straightforward configuration which is easy to calculate.

Figure 21-11 Schematic and analytical circuits for Common-Source FET amplifier.

#### Common-Source WITH a Series Source Resistor

This adds R3 between ground and Source electrode. Voltage gain for ratios of R4:R3 of about 4:1 becomes, approximately:

Voltage Gain

$$\approx \frac{gm \cdot R_L}{1 + R_3 \cdot gm}$$

Input resistance about same as no Source resistor.

#### **Common-Drain or Source-Follower**

This is a slight variation on the typical voltage-follower in that the Gate is Biased slightly Positive relative to the Source. For a P-Type FET the Gate would be Biased slightly negative relative to the Source.

While this has a slightly lower voltage gain, the added negative feedback provides less distortion over the conventional voltage-follower with R2 returned to ground. Typical voltage gains would be 0.5 to 0.8 over the signal source. Needed reciprocals shown in the Figure.

Figure 21-12 Schematic and analytical forms of the *Source-Follower*.

Input Resistance =

$$R_{12} + [(1 + gm R_{12})R_{LOAD}]$$

Input resistance can become **very** large due to the second term-group multiplication.

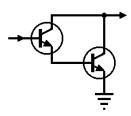

# **Darlington**

Shown in Figure 21-13, the *Darlington* pair was an early method to increase both  $\beta$  and input impedance. Biasing requires twice the Base-Emitter DC voltage and total  $\beta$  is the multiple of all  $\beta$ s. Its name derives from its inventor, Sidney Darlington (1906 - 1997) who received a patent on it at Bell Telephone Labs in 1953.

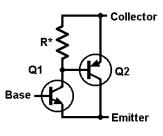

# Sziklai Pair

George C. Sziklai invented a replacement for the Darlington pair in 1957. Seen in Figure 21-14, it works the same as a Darlington. The resistor (marked R\*) is there to handle some of the Collector current from O1. While not much used and of no appreciable advantage, it shows the interchangeability possible between NPNs and PNPs in the same circuit. Connections of Base, Collector, and Emitter refer to the Darlington circuit.

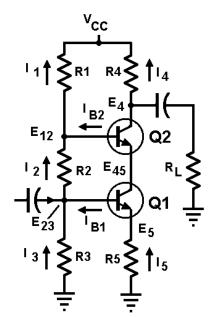

# **BJT Cascode**

Another tube circuit relic revitalized with transistors, the BJT transistor version of Figure 21-15 has a Common-Emitter stage, Q1, directly connected to a Grounded-Base stage, Q2.<sup>13</sup> Frequency response is relatively immune to *Miller Effect*, thus bandpass is the widest.

Emitter-Collector current flows through *both* O1 and O2. As a variation, the Base of Q2 may be connected to another DC source as a current/gain control.<sup>14</sup> To begin, one has to assume an Operating Point somewhere to determine Emitter-Collector current. Initially,  $I_4 \approx I_5$  and the following are true:

$$E_{23} - E_5 = 0.7 V \qquad E_{12} - E_{45} = 0.7 V$$

$$V_{CC} > E_4 \qquad E_4 > E_{12} \qquad E_{45} > E_5$$

Figure 21-13 A Darlington pair.

Figure 21-14 Sziklai pair

Current through the resistor string of R1, R2, R3 should be about Figure 21-15 NPN Cascode.

4 to 10 times the Base current. Voltage to ground at E4 is

around 2/3 of  $V_{cc}$  to insure an adequate AC peak-to-peak output voltage swing. Emitter-to-

<sup>&</sup>lt;sup>13</sup> Etymology of *cascode* is uncertain. Used with tubes in the 1950s, it may be a corruption of cascade.

<sup>&</sup>lt;sup>14</sup> An article in QST, December 2007, entitled *The Hybrid Cascode - A General Purpose AGC IF* Amplifier, by Hayward and Damm, for a 100 db gain control in a superheterodyne receiver last IF. It used FETs for Q1 and BJTs for Q2 in each stage..

Collector voltage of both Q1 and Q2 should be greater than about 0.3 V to avoid clipping at AC. Note that R5 may be deleted. If so, E23 is 0.7 VDC. The capacitor at input, going to E23, is there as a reminder that, at DC, capacitors are open-circuits at DC. Choosing an Emitter current and setting I3 at about 10 times Base current is a beginning point; let Vcc = 18 VDC, Emitter current equal 2 mA,  $\beta$  equals 120 and Base current ~ 16 2/3  $\mu$ A:

Let R5 = 1.2 KOhms so that E5 ~ 2.4 VDC (all or part of R5 can be bypassed for AC)  $E_{23} \sim 3.1$  VDC and, if  $I_3 \sim 167 \mu$ A, then R3 ~ 18 KOhms E4 would be roughly 2/3 of Vcc so R4 can be about 2.7 KOhms for E4 = 6.6 VDC  $E_{45}$  will then be somewhere between about 7 VDC and 4 VDC Choosing  $E_{12}$  at about 5.3 VDC would make R2 ~ 12 KOhms ( $I_2$  is ~ 184  $\mu$ A) As a result,  $E_{45}$  is about 4.6 VDC (holding to 5.3 V - 0.7 V) ( $V_{CC} - E_{12}$ ) = 6.7 V and  $I_1$  is about 200  $\mu$ A; R1 will be about 33 KOhms.

For AC mid-band, the junction of R1, R2, and Q2 Base is bypassed to ground by a capacitor. The Emitter of Q1 may go directly to ground (no R5) or it may be split into R5A (smaller) and R5B (larger), both in series. Mid-passband responses:

Voltage Gain =  $R_L / (r_E + R_{5A})$   $R_L^{'} = R4 || R_L$   $r_E = (26 \times 10^{-3}) / I_5$ Input Resistance =  $R2 || R3 || R_N$   $R_N = \beta (r_E + R5_A)$

Output Resistance = R4

Given the previous values with R5 split so that R5A = 56 and R5B = 1.2 KOhms,  $R_L = 10$  K, the Voltage gain will be 30.8 times, Input Resistance = 3850 Ohms, Output Resistance = 2700 Ohms.

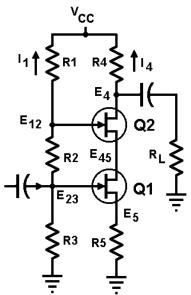

# **FET Cascode**

The FET version of the cascode is given in Figure 21-16. Most statements of the cascode of Figure 21-14 apply here but with some exceptions. Q2 Gate is bypassed to ground but can be used as a voltage-driven gain control.

For AC mid-passband small-signal operation, the following applies:

Output Voltage Gain =  $gm (R4 || R_L)$

Output Resistance = R4

Input Resistance = (R2 || R3)

Figure 21-16 An FET Cascode, similar to Figure 21-14.

Radio Hobbyists Designbook

# Semiconductor Design Basics

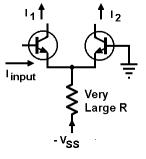

# **Differential Amplifiers**

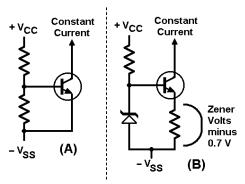

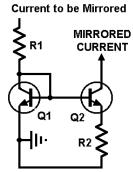

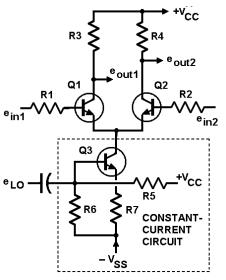

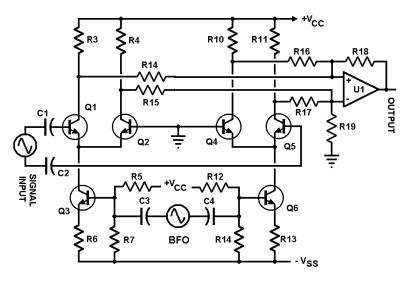

Figure 21-17 Ideal Differential circuit.